Principle¶

Boards¶

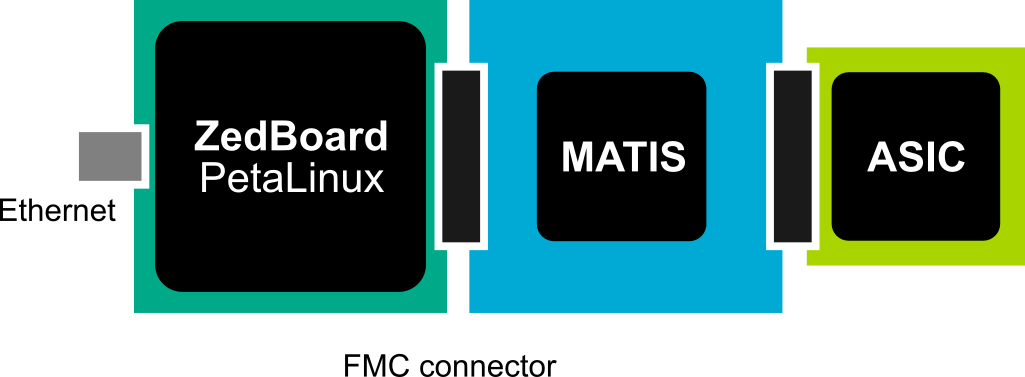

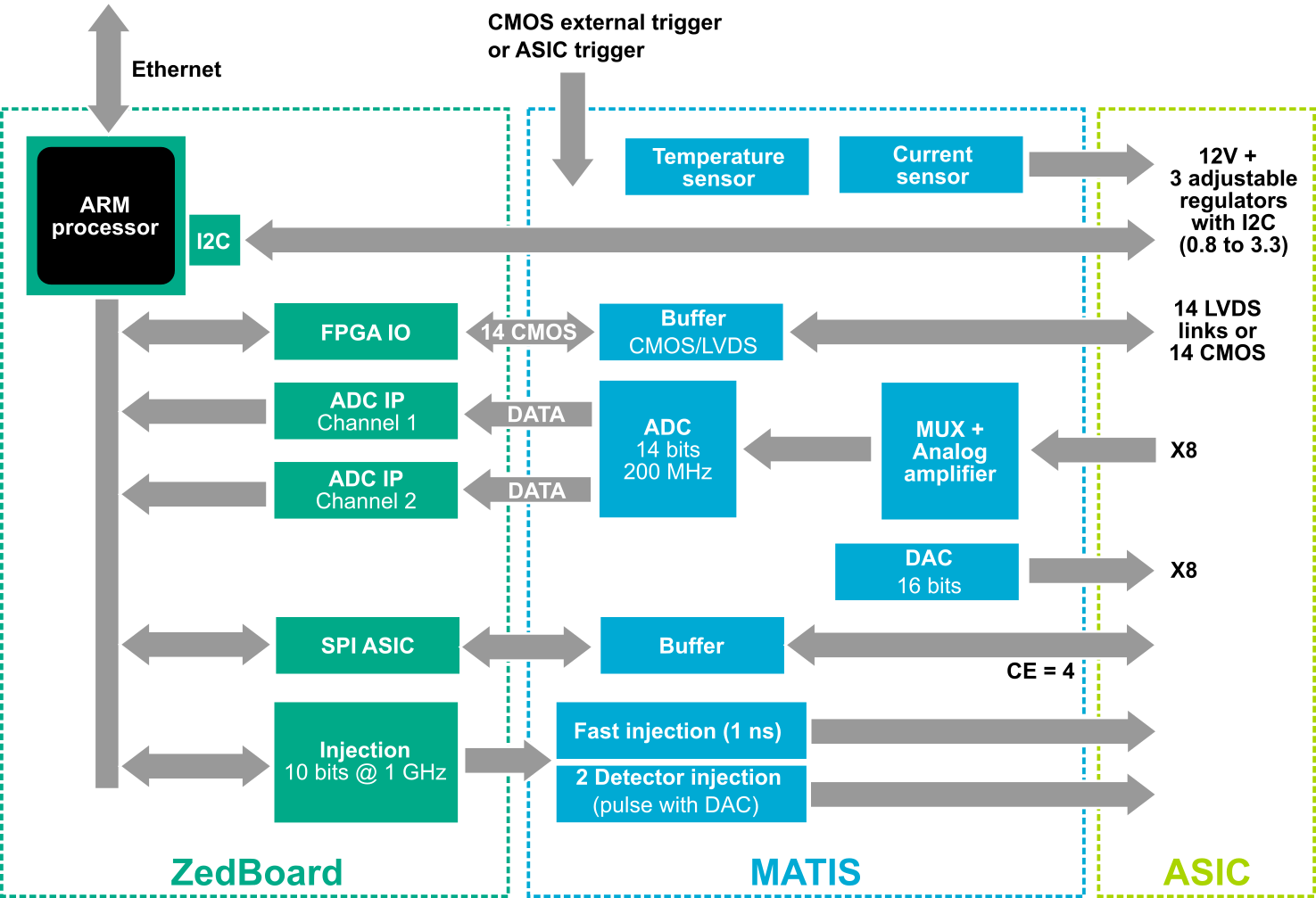

The test bench consists of three boards:

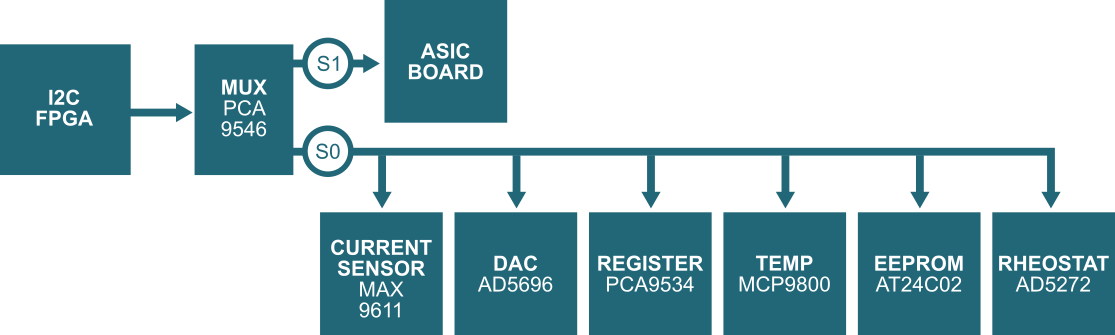

ZedBoard: Using a Xilinx Zynq®-7000 SoC, it provides all necessary interfaces to control the others boards like ethernet connection, I2C interface, power supply

MATIS board:

ASIC board:

Functional scheme¶

FMC connector¶

Pin |

Function |

|---|---|

VCC_ASIC_LOGIC |

Regulated voltage |

VCC_ANALOGIQUE_ASIC_1 |

Regulated voltage |

VCC_ANALOGIQUE_ASIC_1 |

Regulated voltage |

VCC_12V |

12 V from main power, fuse protected |

ASIC_SDA and SCL |

IC2 link |

RESET_ASIC |

Pull down by default. |

SC_ASIC |

|

LVDS_CLK_TO_ASIC |

Clock from FPGA to ASIC |

TRIGGER_TO_ASIC |

|

TRIGGER_FROM_ASIC |

|

HSEC8_ASIC_BUFFER |

|

INJ_DETECTOR |

|

INJ_NS |

|

ASIC_DATA |

Data from ASIC connected to ADC |

DAC_ASIC |